# TRAVELING THREADS: A NEW MULTITHREADED EXECUTION MODEL

A Dissertation

Submitted to the Graduate School of the University of Notre Dame in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy

by

Richard Cameron Murphy, M.S., B.S., B.A.

Peter M. Kogge, Director

Graduate Program in Computer Science and Engineering

Notre Dame, Indiana

June 2006

# TRAVELING THREADS: A NEW MULTITHREADED EXECUTION MODEL

Abstract

by

Richard Cameron Murphy

Computer architecture is plagued by the von Neumann bottleneck. This work introduces and evaluates the *traveling thread* execution model in which threads migrate to the memory resources close to the data they require rather than perform remote memory accesses. This helps address the von Neumann problem by exposing additional concurrency within programs to tolerate long memory latencies, reduces two-way request/response network transactions typical of caching architectures to one way thread migration transactions, and reduces or eliminates cache coherency traffic. For Sarah, who always inspires me.

# CONTENTS

| FIGUR                      | ES              |                                                                          | • | • |   | • | vii                                                                                 |

|----------------------------|-----------------|--------------------------------------------------------------------------|---|---|---|---|-------------------------------------------------------------------------------------|

| TABLE                      | S               |                                                                          | • |   |   |   | xii                                                                                 |

| ACKNO                      | OWLEI           | OGMENTS                                                                  | • |   |   |   | xiii                                                                                |

| CHAPT<br>1.1<br>1.2<br>1.3 | The P<br>Object | INTRODUCTION                                                             | • | • | • | • | $     \begin{array}{c}       1 \\       5 \\       10 \\       12     \end{array} $ |

| CHAPT                      | FER 2:          | THE STATE OF THE ART CONCISELY DEFINED .                                 |   |   |   |   | 13                                                                                  |

| 2.1                        | Analy           | sis and Simulation Methodology                                           |   |   |   |   | 13                                                                                  |

|                            | 2.1.1           | Amber                                                                    |   |   |   |   | 14                                                                                  |

|                            | 2.1.2           | Validation                                                               |   |   |   |   | 16                                                                                  |

| 2.2                        |                 | ssing-In-Memory (PIM) $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$ |   |   |   |   | 17                                                                                  |

|                            | 2.2.1           | The Architecture of Other Large-scale PIM Efforts                        |   |   |   |   | 18                                                                                  |

|                            | 2.2.2           | A PIM's View of Memory                                                   |   |   |   |   | 19                                                                                  |

|                            | 2.2.3           | Technology and Performance                                               |   |   |   |   | 20                                                                                  |

|                            | 2.2.4           | Microarchitecture Considerations and Memory Layout                       |   |   |   |   | 22                                                                                  |

|                            | 2.2.5           | Execution Model Fundamentals: Parcels                                    |   |   |   |   | 24                                                                                  |

|                            | 2.2.6           | Instruction Set Architecture Issues                                      |   |   |   |   | 25                                                                                  |

| 2.3                        |                 | bystems                                                                  |   |   |   |   | 26                                                                                  |

|                            | 2.3.1           | НТМТ                                                                     |   |   |   |   | 26                                                                                  |

|                            | 2.3.2           | DIVA                                                                     |   |   |   |   | 27                                                                                  |

|                            | 2.3.3           | BlueGene/C                                                               |   |   |   |   | 27                                                                                  |

| 2.4                        | 2.3.4           | Impulse                                                                  |   |   |   |   | 27                                                                                  |

| 2.4                        |                 | el Processor and Memory Architectures                                    |   |   |   |   | 27                                                                                  |

|                            | 2.4.1           | DSMs and SMPs                                                            |   |   |   |   | 28                                                                                  |

|                            | 2.4.2           | Massively Parallel Processors (MPPs)                                     |   |   |   |   | 28                                                                                  |

|                            | 2.4.3           | Vector Pipeline Machines                                                 |   |   |   |   | 29                                                                                  |

|                            | 2.4.4           | NUMA and CC-NUMA Architectures                                           |   |   |   |   | $\frac{30}{20}$                                                                     |

|                            | 2.4.5           | COMA Machines                                                            |   |   |   |   | 32                                                                                  |

|                            | 2.4.6           | Memory Consistency Models                                                | • | • | · | • | 34                                                                                  |

| 2.5   | Threads and Multithreading                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 37 |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|       | 2.5.1 Simultaneous Multithreaded Architectures (SMTs)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . 39 |

|       | 2.5.2 Cray Multithreaded Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |

|       | 2.5.3 Thread Migration: Active Messages and the J-Machine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |

|       | 2.5.4 Active Pages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |

| 2.6   | Programming Models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |

|       | 2.6.1 Imperative Models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 46 |

|       | 2.6.2 Functional Models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 47 |

|       | 2.6.3 Actor Based Languages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |

| 2.7   | Conclusions and Architectural Relevance to PIM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| 2.1   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 00 |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |

| CHAPT | FER 3: BENCHMARKS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 51 |

| 3.1   | Methodology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |

| 3.2   | Floating Point Benchmarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |

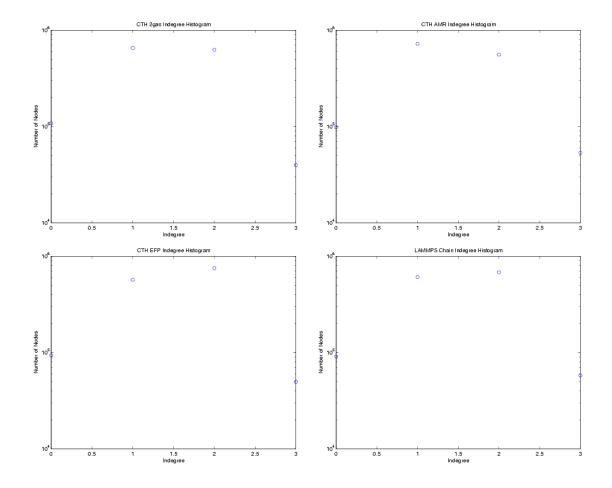

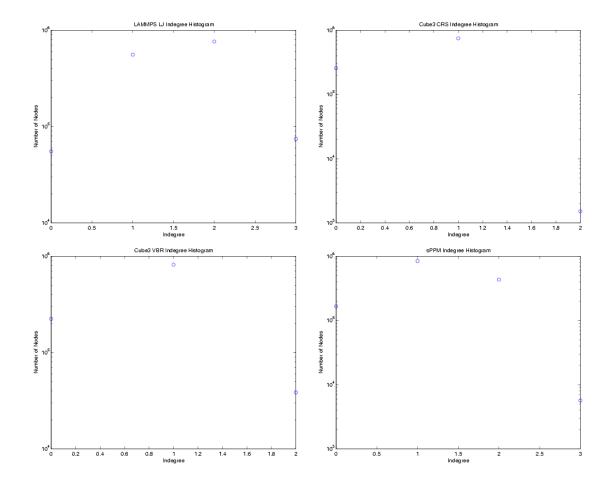

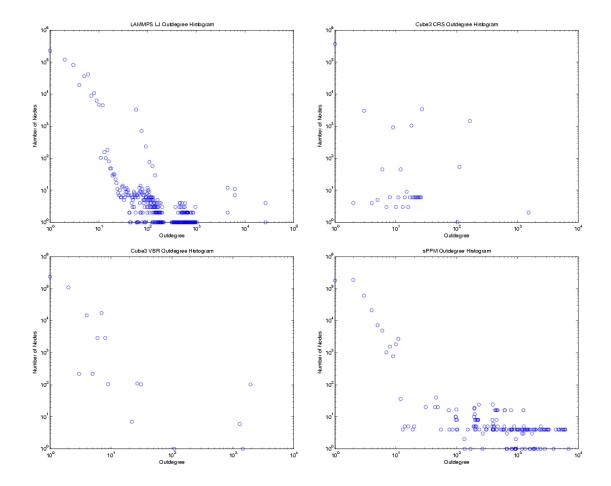

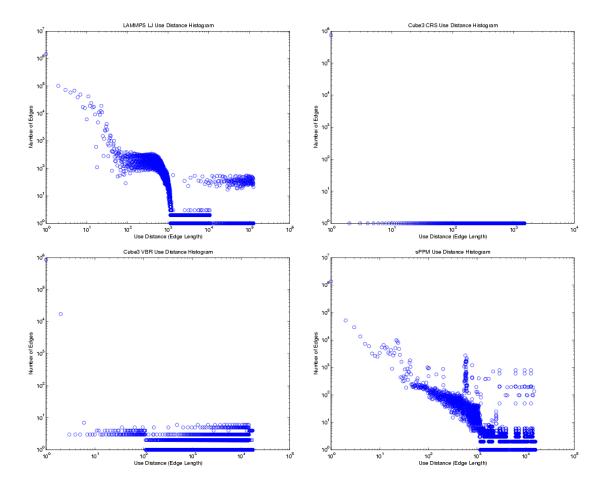

| 0.2   | 3.2.1 LAMMPS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |

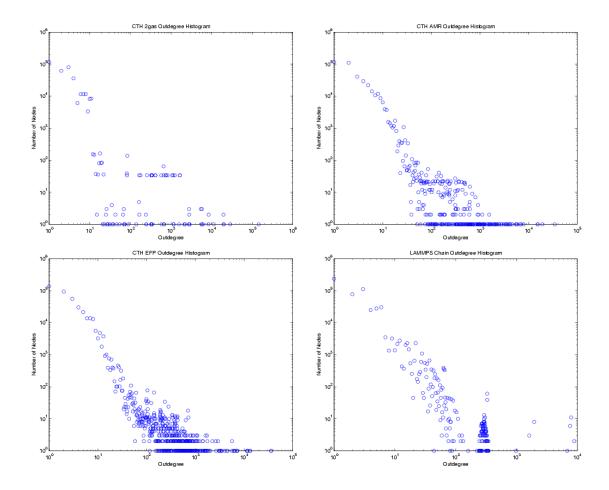

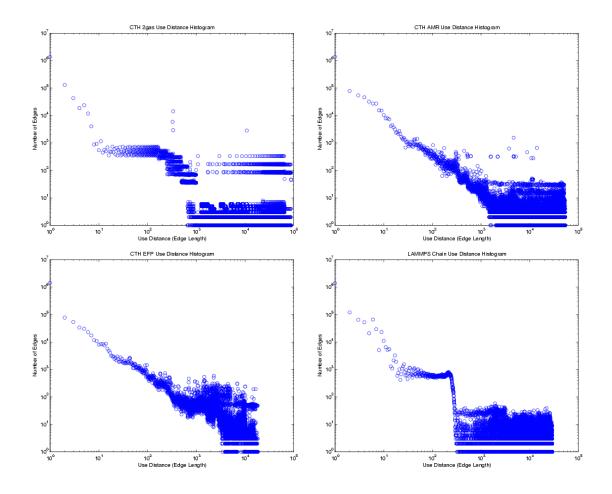

|       | 3.2.2 CTH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |

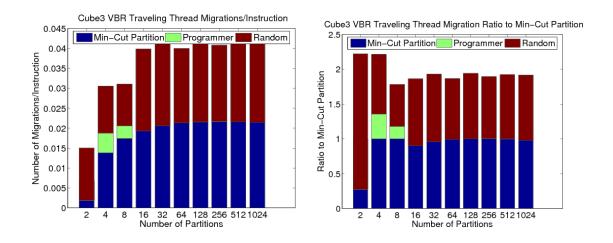

|       | 3.2.3 Cube3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |

|       | 3.2.4 sPPM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |

| 3.3   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |

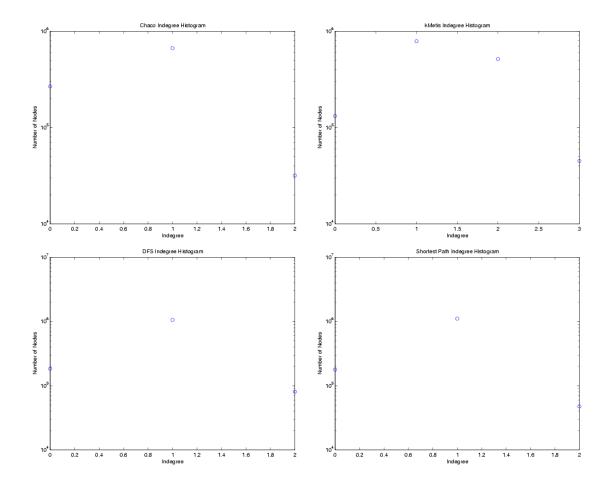

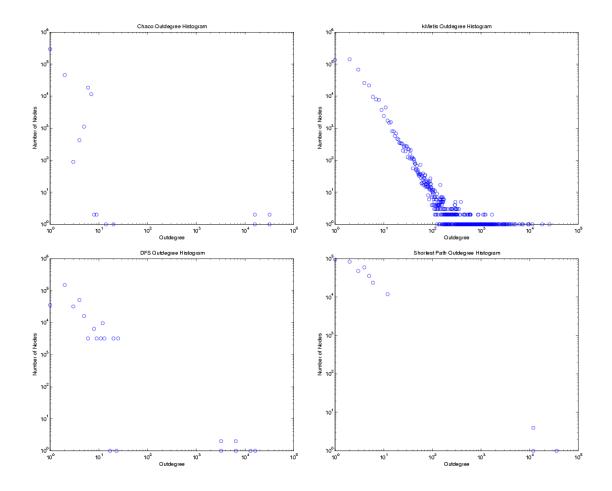

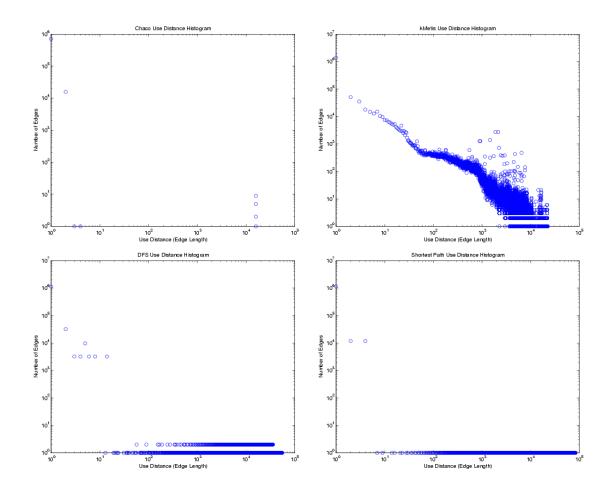

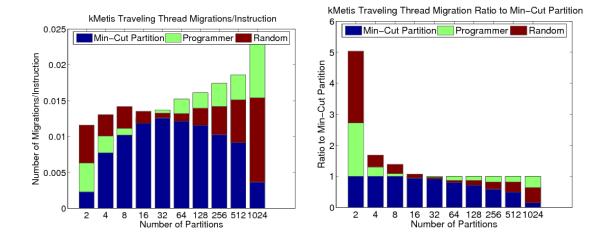

| J.J   | Integer Benchmarks       3.3.1       Graph Partitioning       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1       3.1 <td></td> |      |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |

|       | 1 ( )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |

|       | 3.3.3 Shortest Path                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 57 |

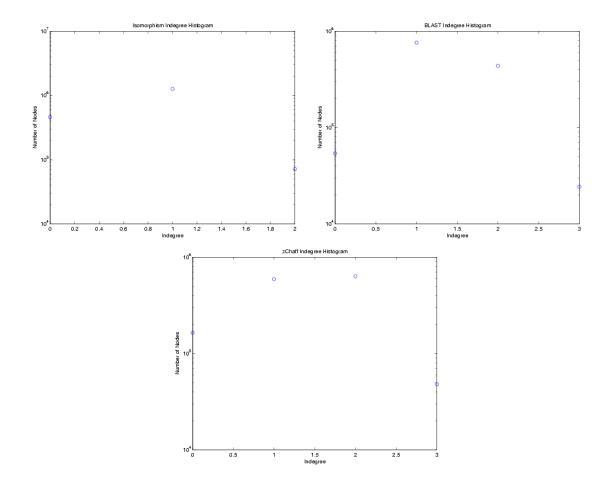

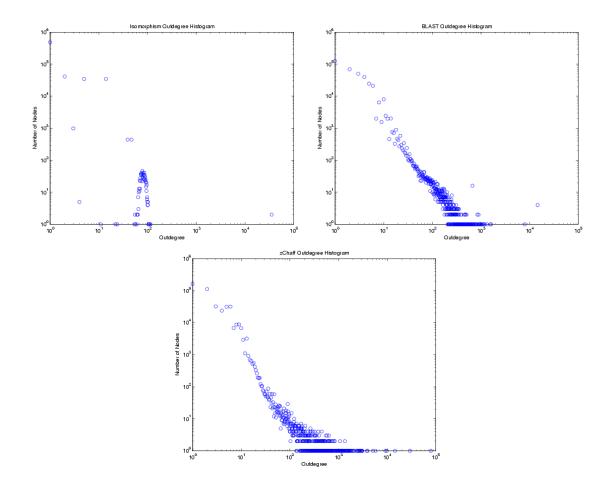

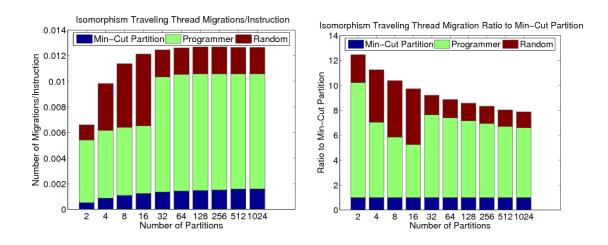

|       | 3.3.4 Isomorphism                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |

|       | 3.3.5 BLAST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |

|       | 3.3.6 zChaff                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |

| 3.4   | SPEC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |

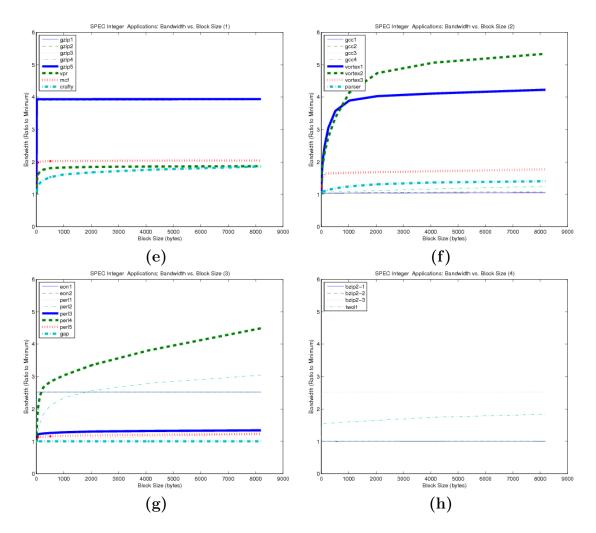

|       | 3.4.1 SPEC Integer Benchmarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |

|       | 3.4.2 SPEC Floating Point Benchmarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 60 |

| 3.5   | Mean Performance Computation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 61 |

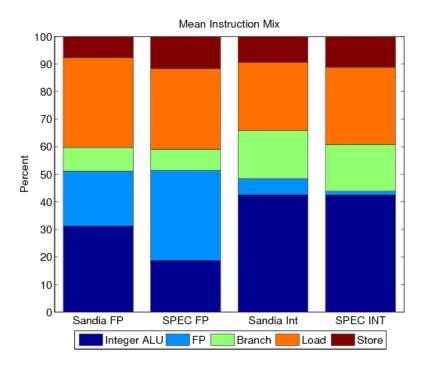

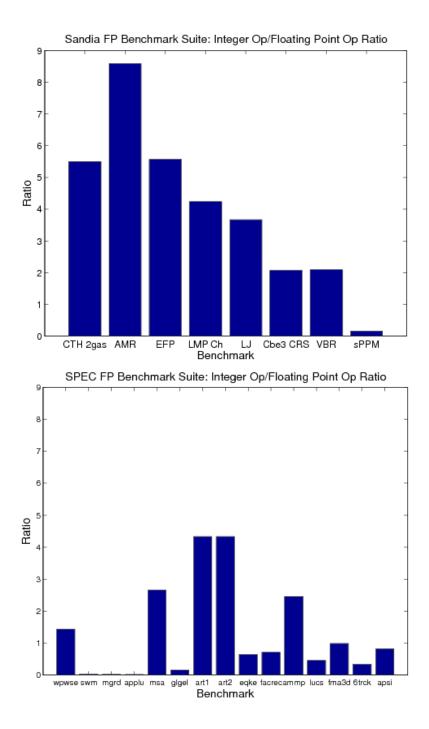

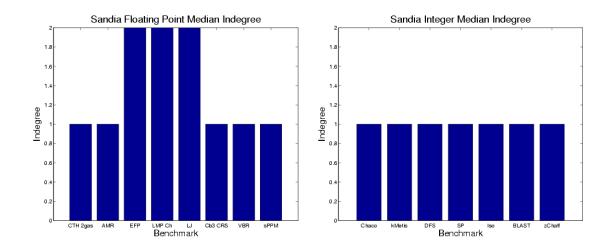

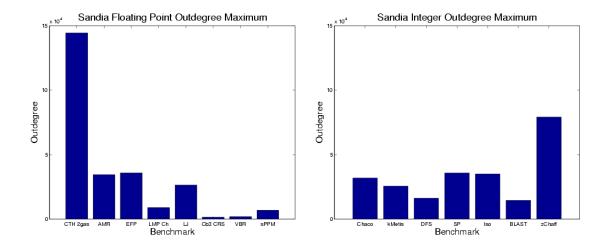

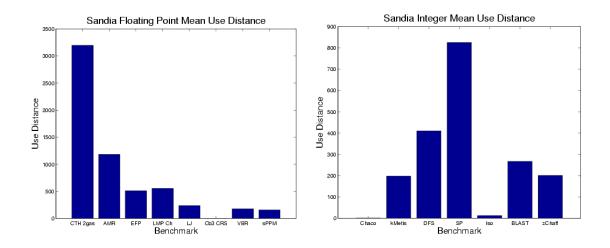

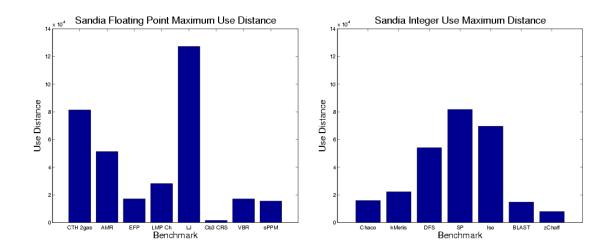

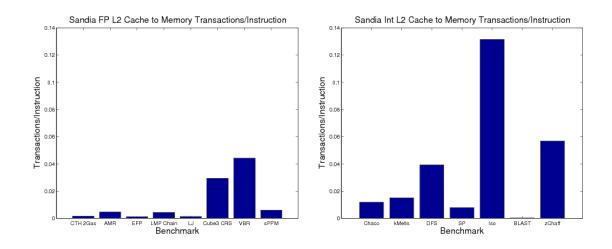

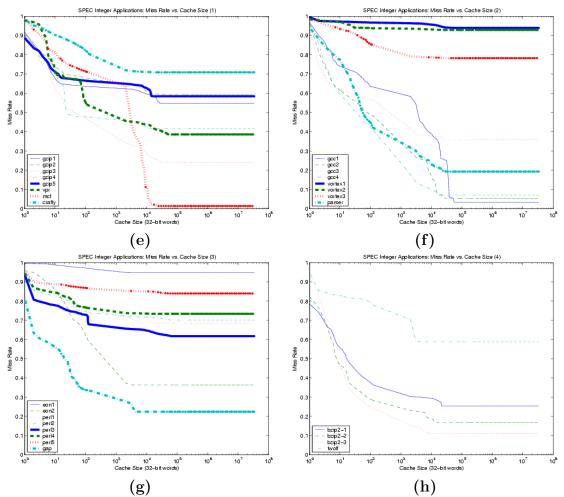

|       | 3.5.1 Initial Observations of Program Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . 62 |

| 3.6   | Temporal Working Set Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |

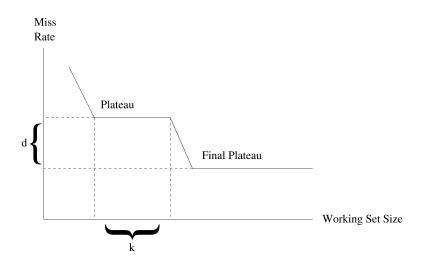

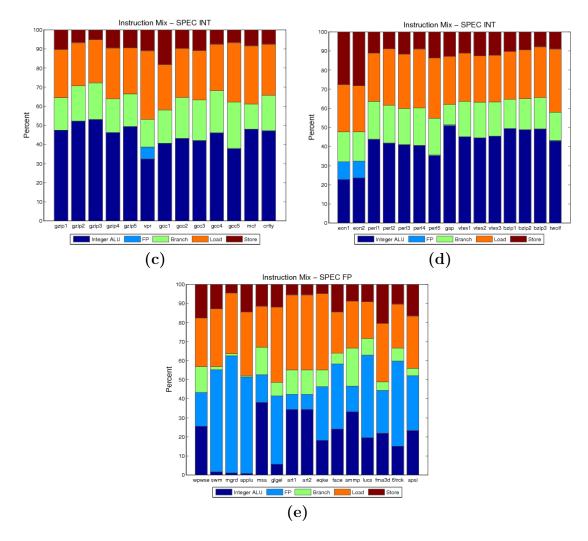

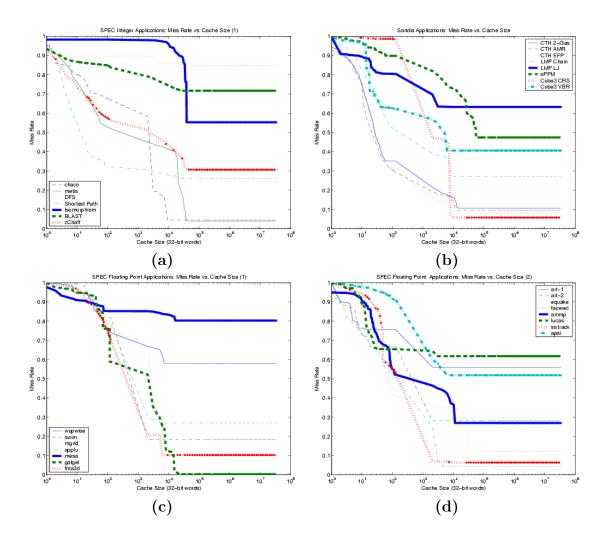

|       | 3.6.1 Miss Rate Interpretation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 66 |

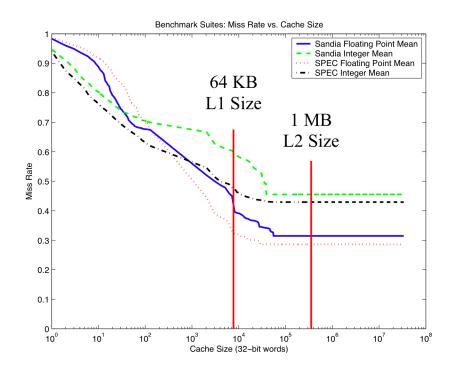

|       | 3.6.2 Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |

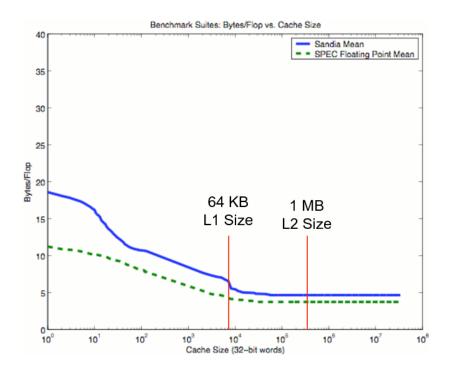

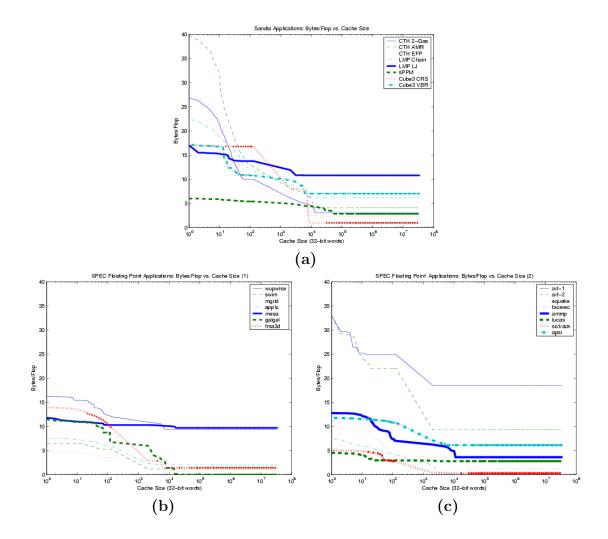

|       | 3.6.3 Bandwidth per Flop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |

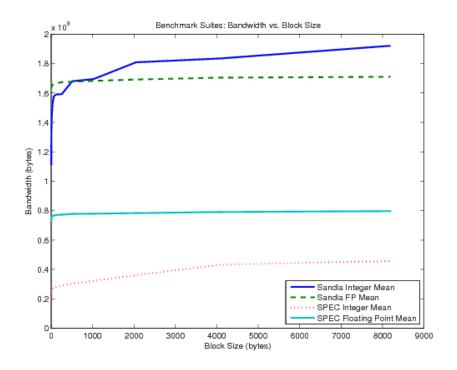

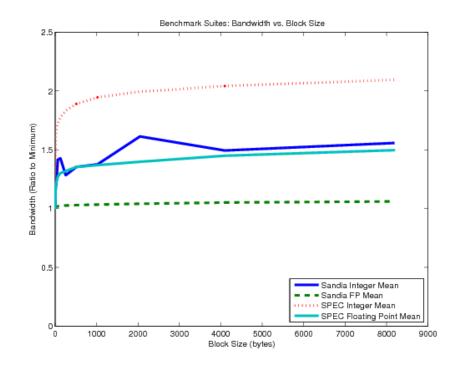

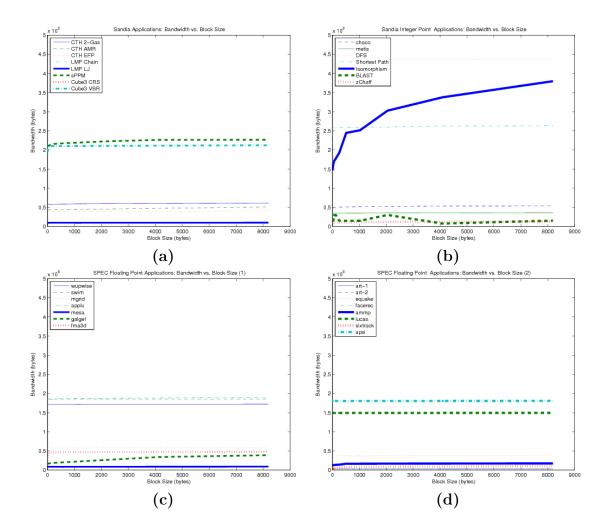

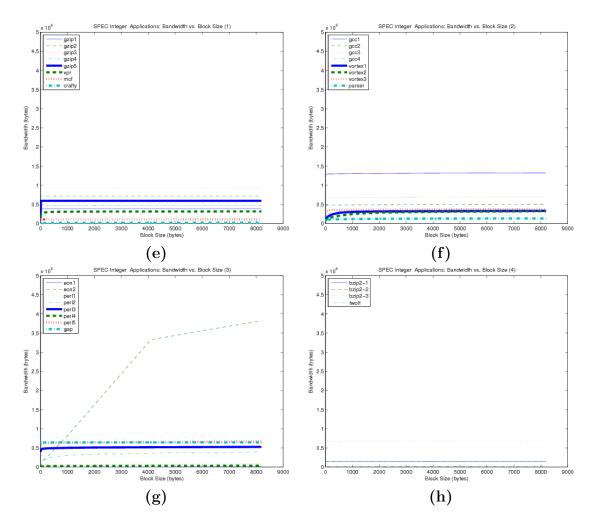

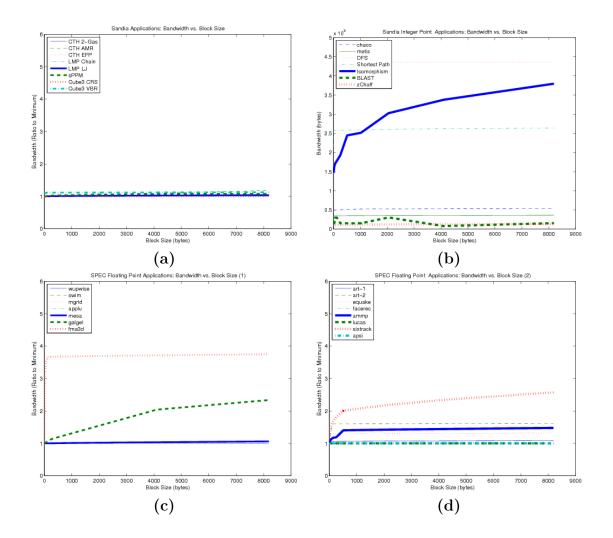

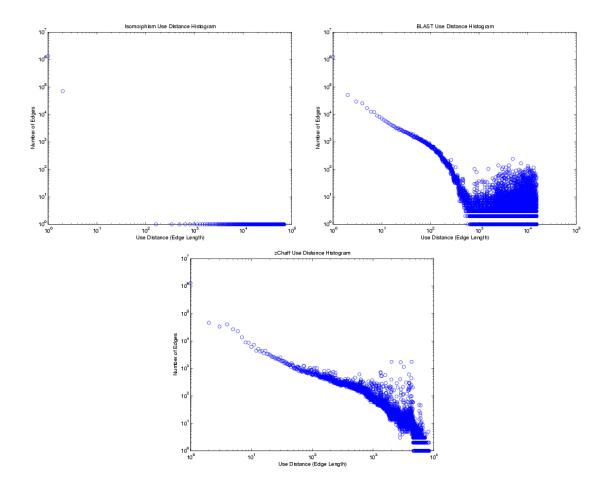

| 3.7   | Spatial Locality Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |

| 3.8   | Conclusions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |

| 0.0   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |

| CHAPT | FER 4: THE TRAVELING THREAD EXECUTION MODEL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 74 |

| 4.1   | The Implications of Prior Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

|       | 4.1.1 Prior Benchmarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |

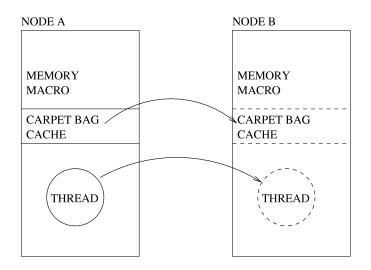

|       | 4.1.2 The Original Carpetbag Cache                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |

|       | 4.1.3 Relevance to the Current Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 80 |

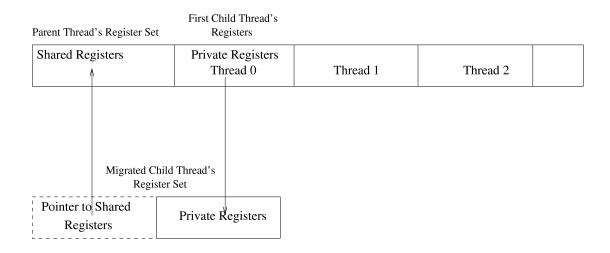

| 4.2   | The Execution Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |

| 7.4   | 4.2.1 An Example Thread                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |

|       | 4.2.1 An Example Thread                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 81 |

|       | 4.2.2 When to imprate, the imprations of Fork and John 4.2.3 Naming and Name Resolution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |

|       | 4.2.4 Thread State                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 86 |

|       | 4.2.5 Synchronization                                                                                                                                       |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.3   | Conclusions                                                                                                                                                 |

|       |                                                                                                                                                             |

|       |                                                                                                                                                             |

|       | TER 5: DATAFLOW                                                                                                                                             |

| 5.1   | Dataflow Graphs                                                                                                                                             |

|       | 5.1.1 Dataflow Graph Construction                                                                                                                           |

|       | 5.1.2 Scheduling $\ldots \ldots 96$                                                   |

|       | 5.1.3 Topological Layering                                                                                                                                  |

| 5.2   | Results                                                                                                                                                     |

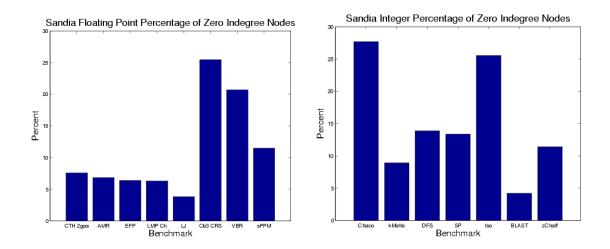

|       | 5.2.1 Dataflow Graph Inputs                                                                                                                                 |

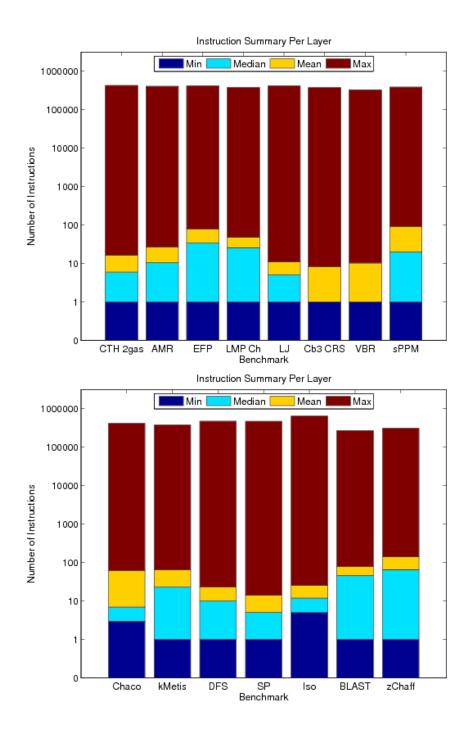

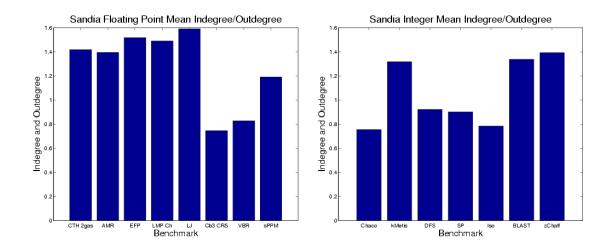

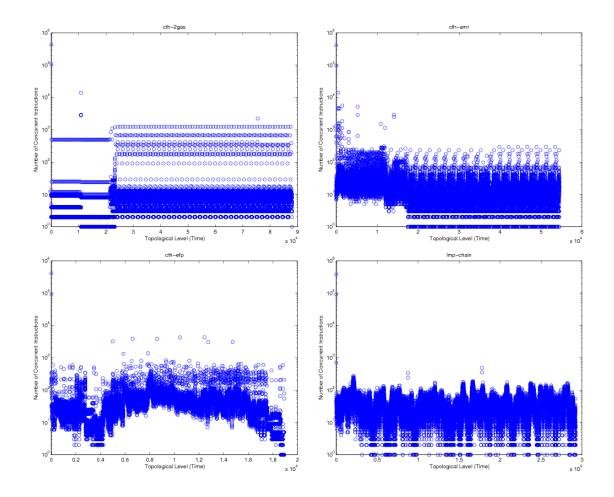

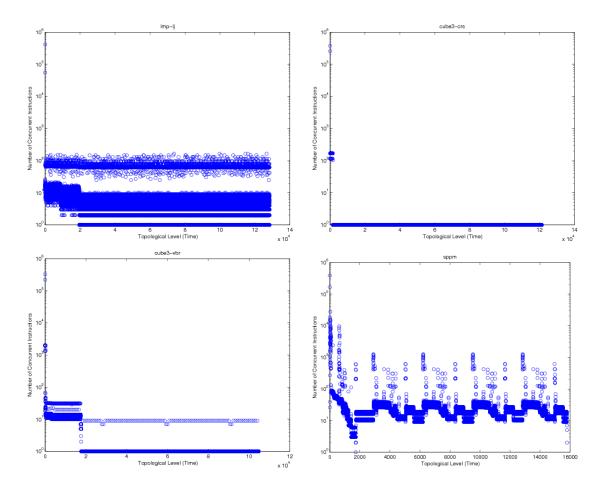

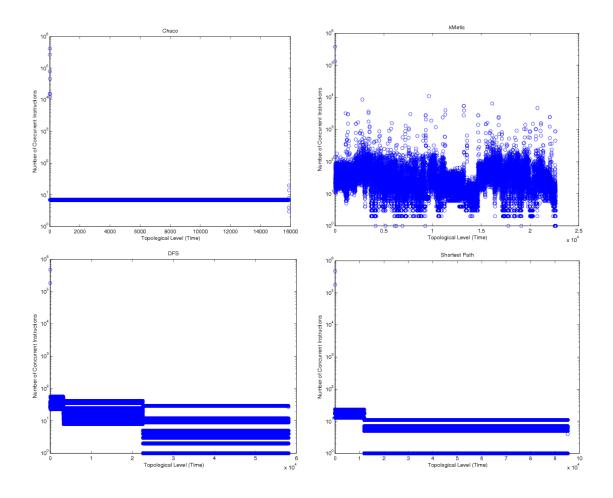

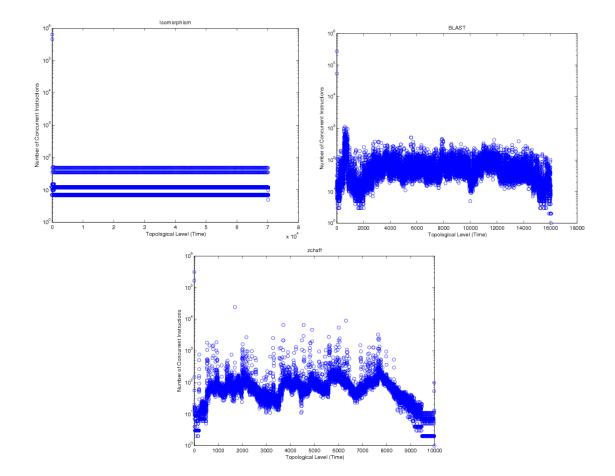

|       | 5.2.2 Concurrency                                                                                                                                           |

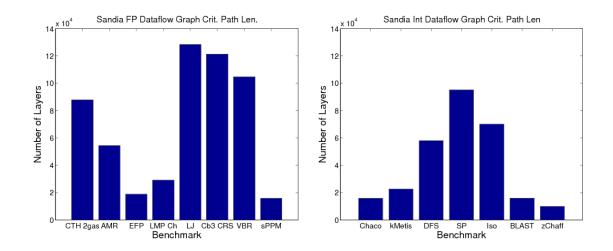

|       | 5.2.3 Latency                                                                                                                                               |

|       | 5.2.4 Data Reuse                                                                                                                                            |

|       | 5.2.5 Data Longevity $\ldots \ldots \ldots$ |

| 5.3   | Conclusions                                                                                                                                                 |

|       |                                                                                                                                                             |

|       |                                                                                                                                                             |

| СНАРТ | $\mathbf{ER} \; 6: \; \mathbf{THREADS} \; \ldots \; $                       |

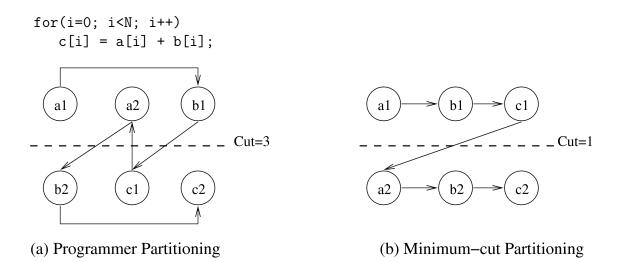

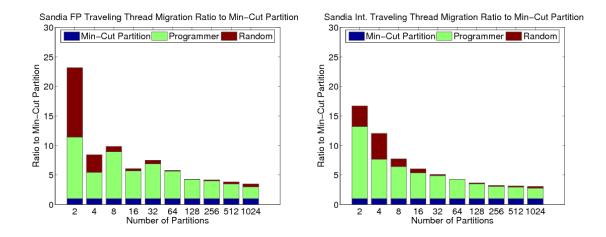

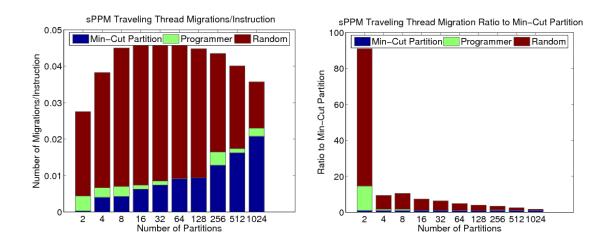

| 6.1   | Minimum Cut Graph Partitioning                                                                                                                              |

| 6.2   | Experimentation                                                                                                                                             |

| 6.3   | Results                                                                                                                                                     |

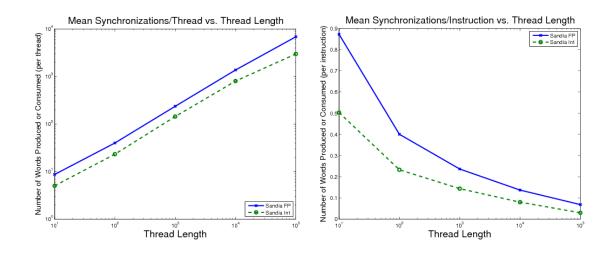

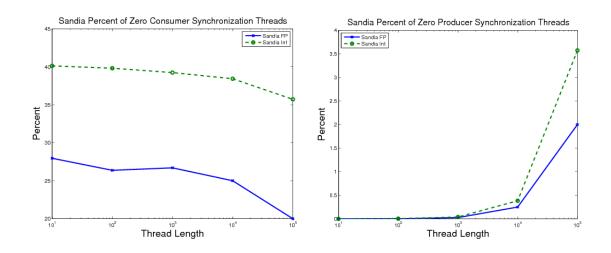

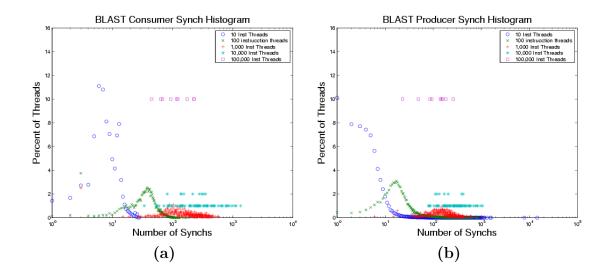

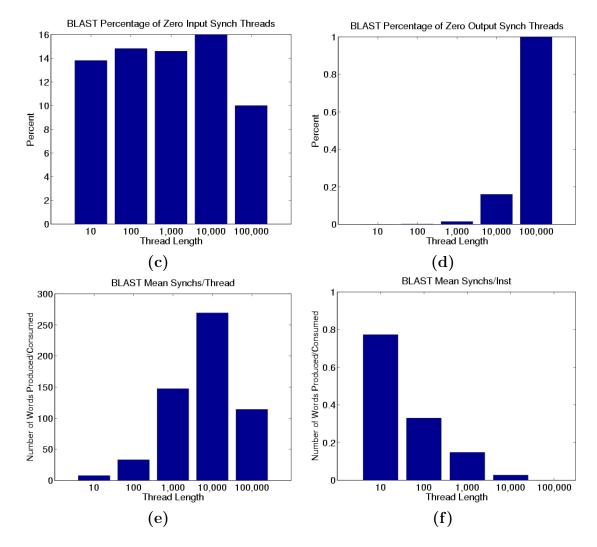

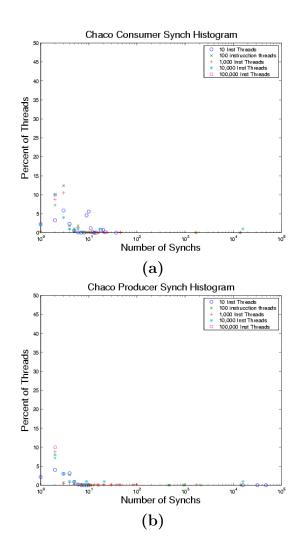

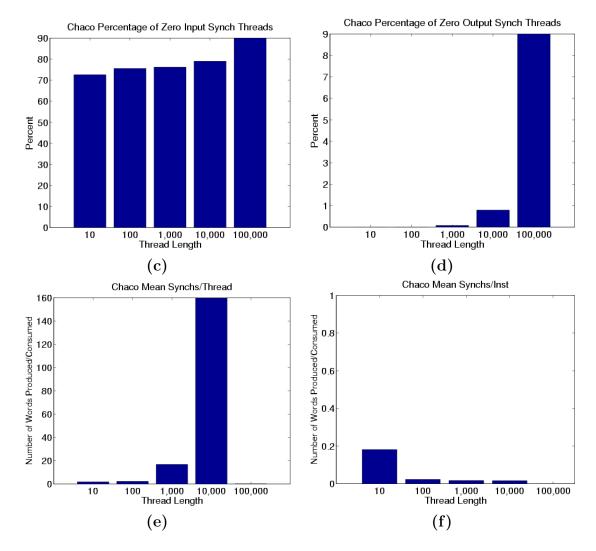

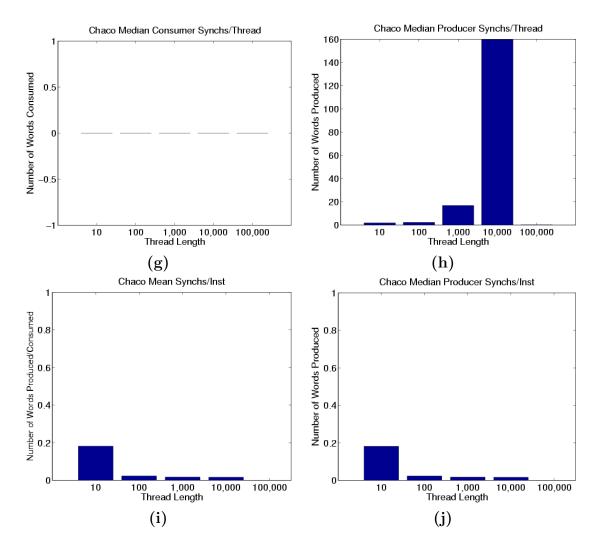

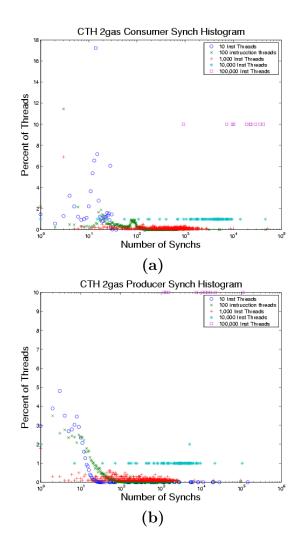

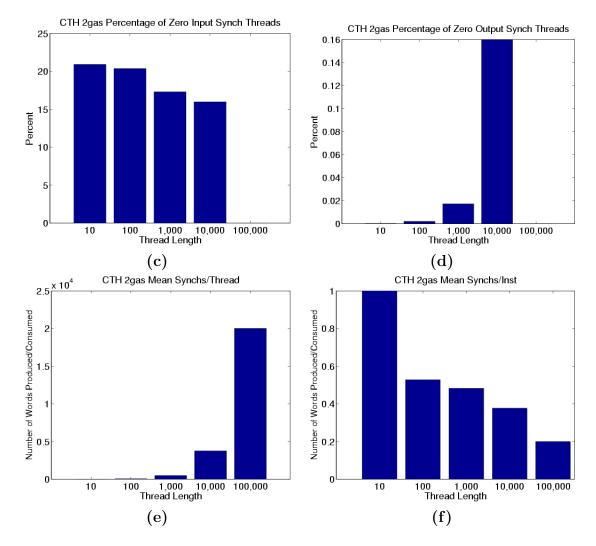

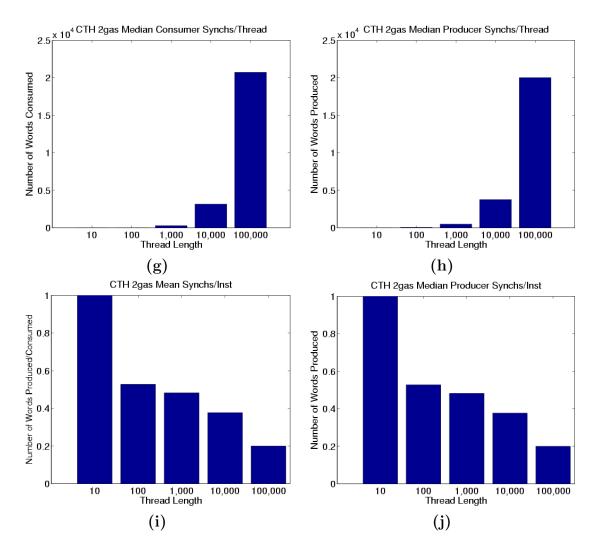

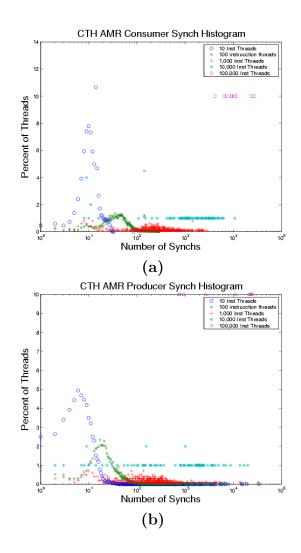

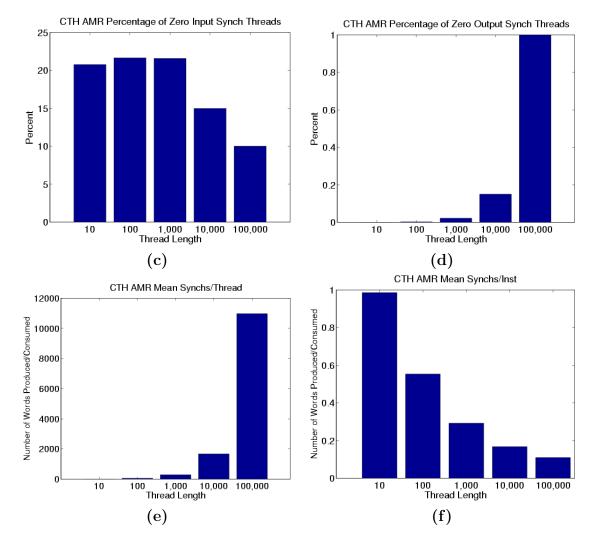

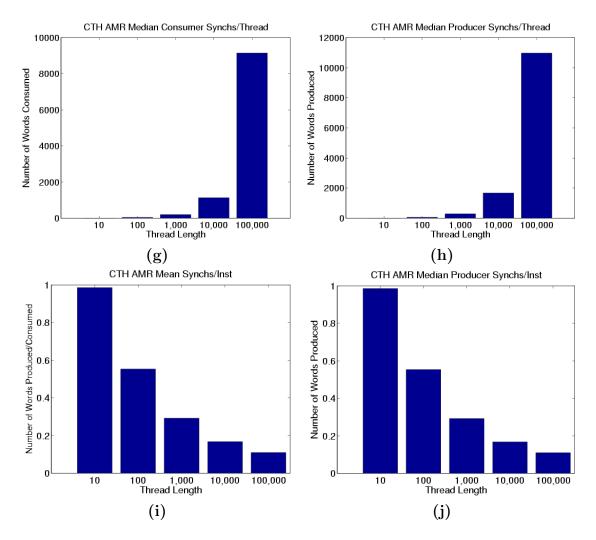

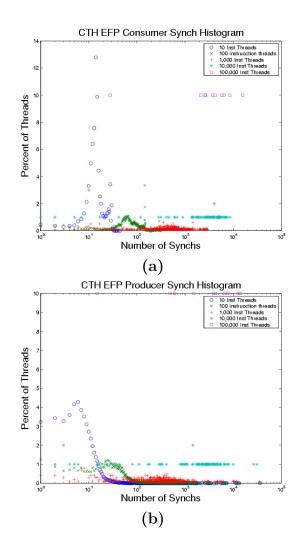

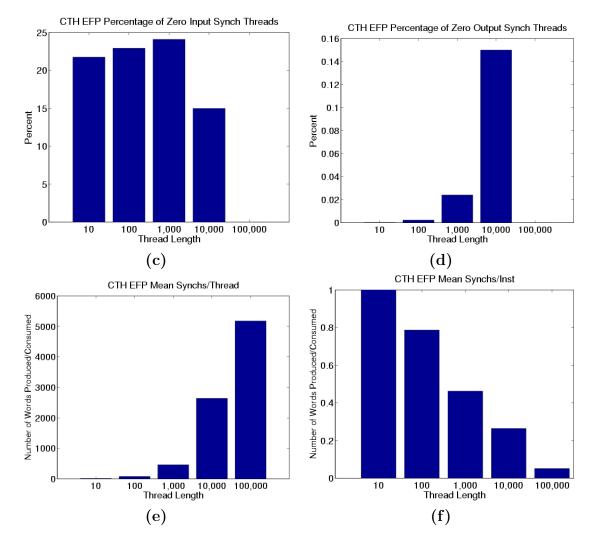

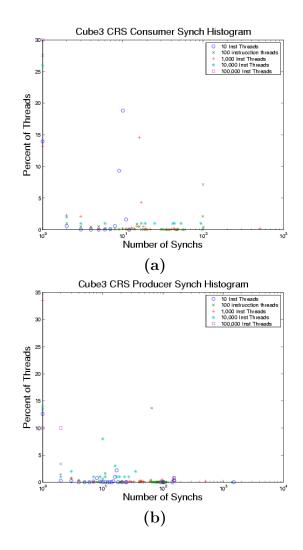

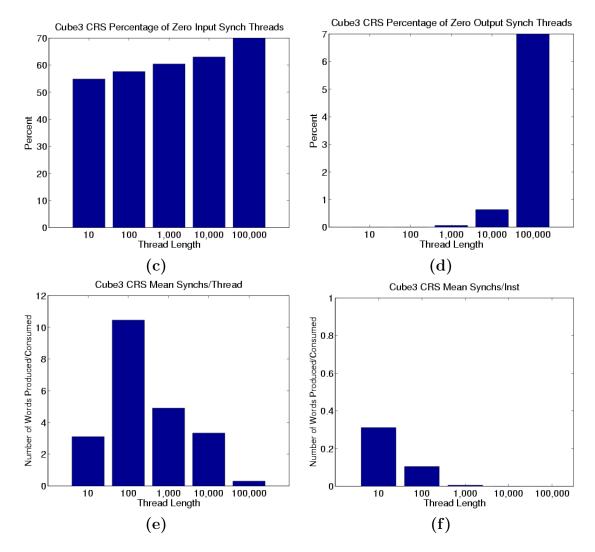

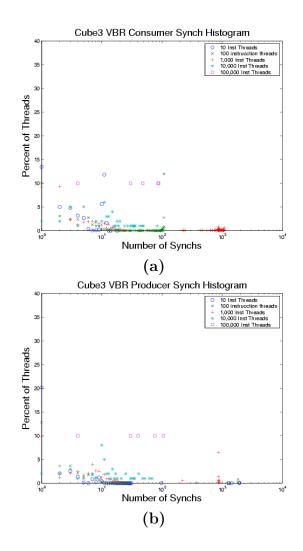

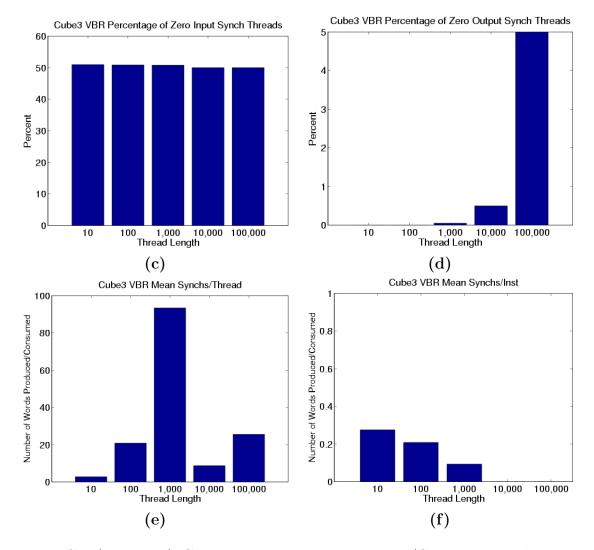

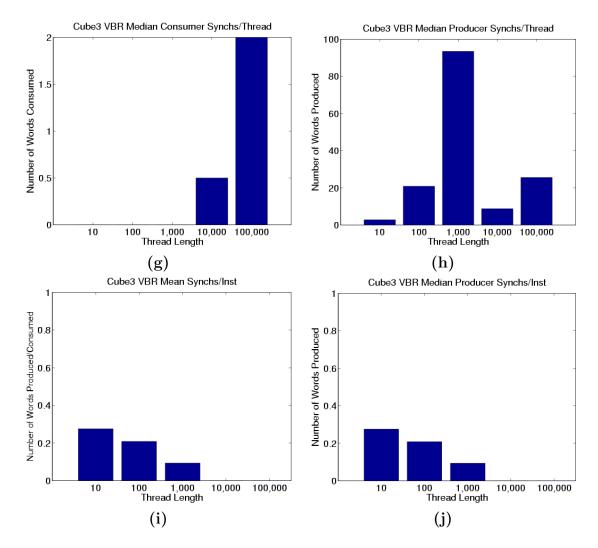

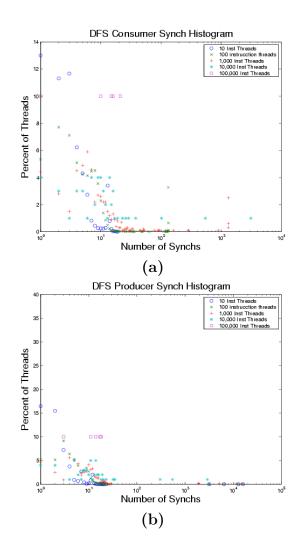

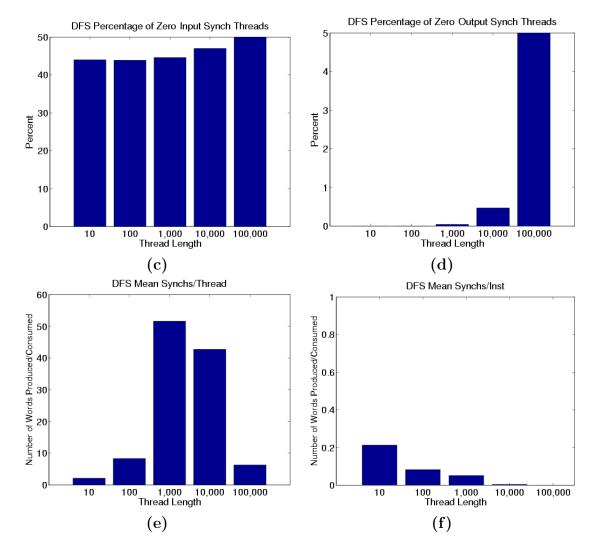

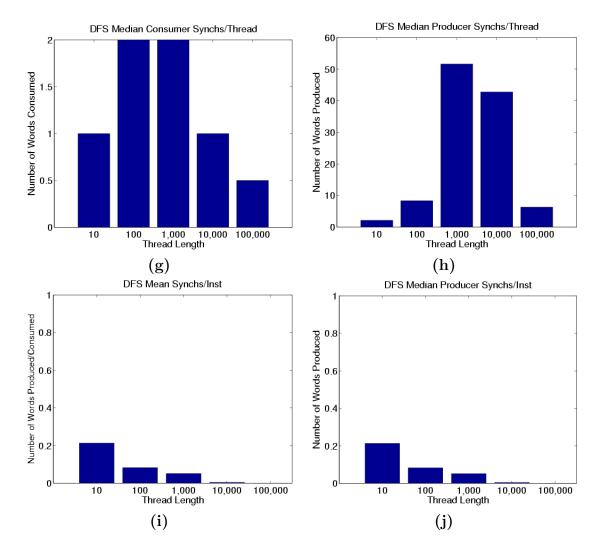

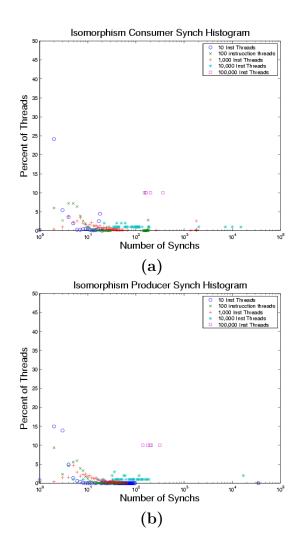

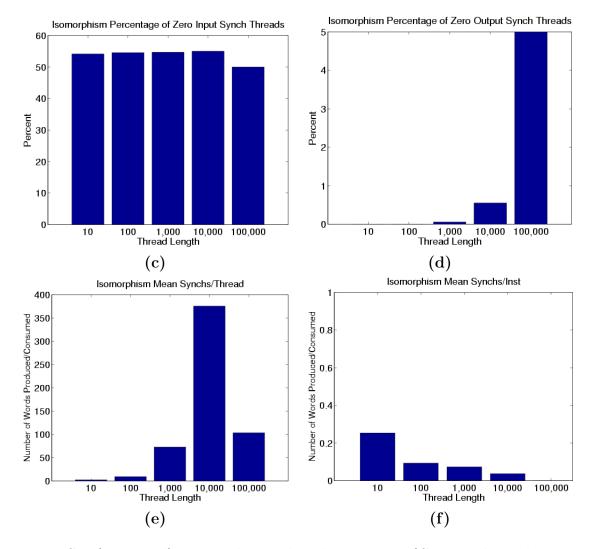

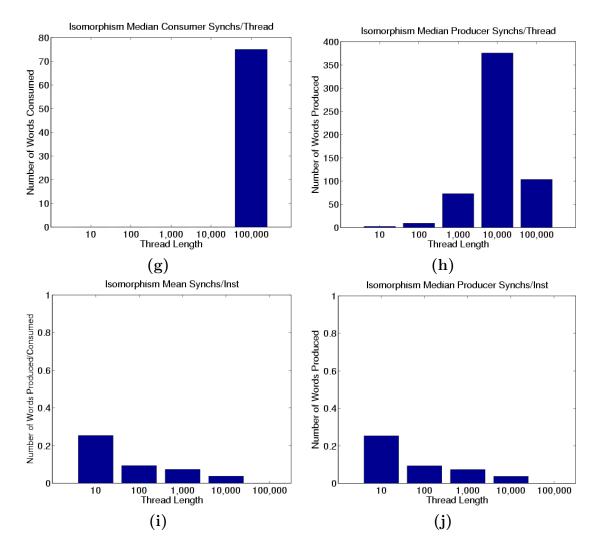

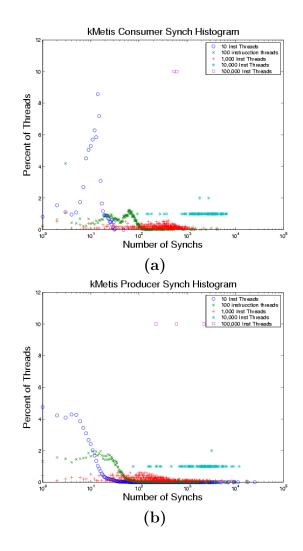

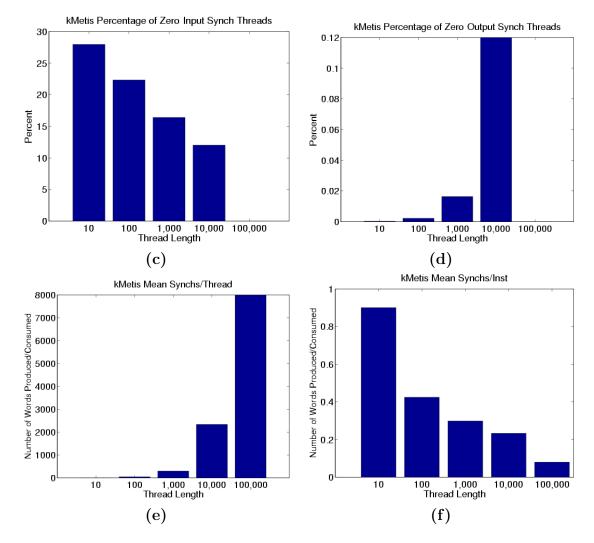

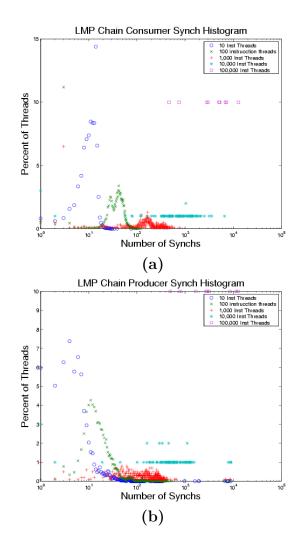

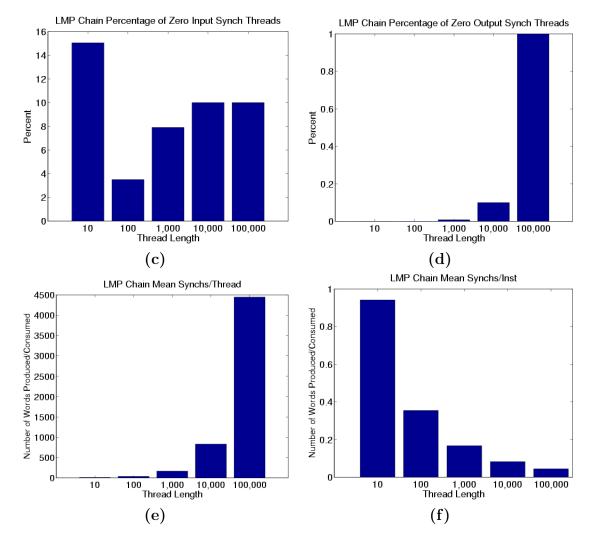

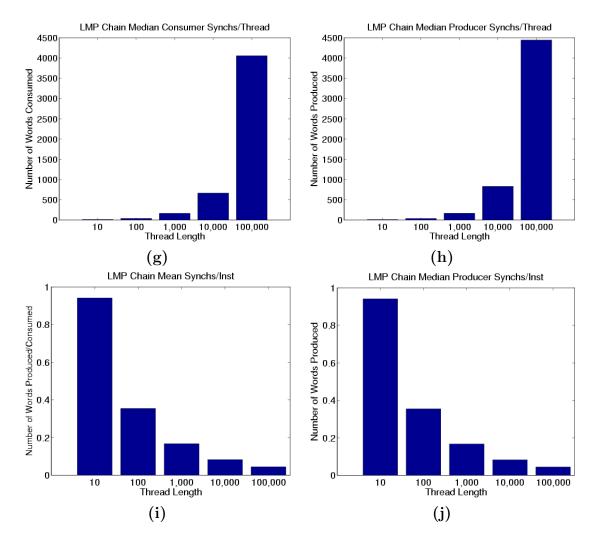

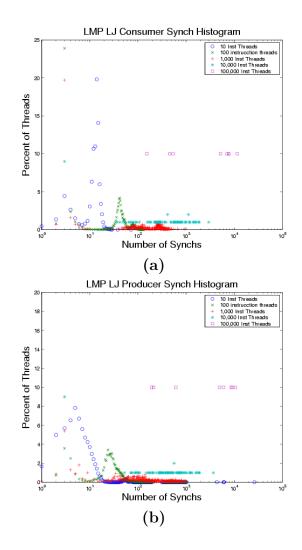

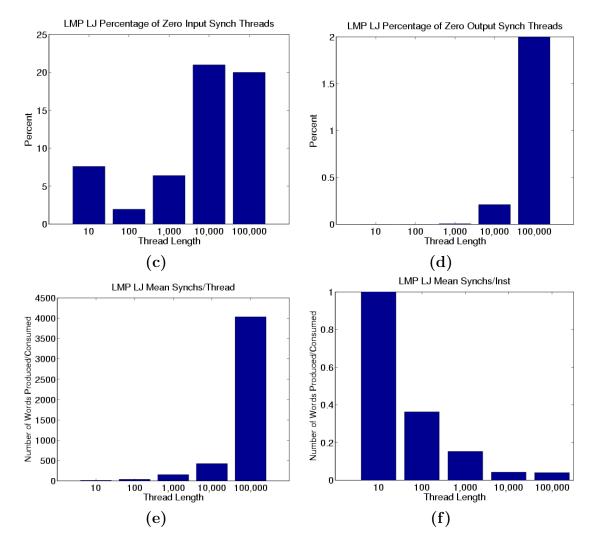

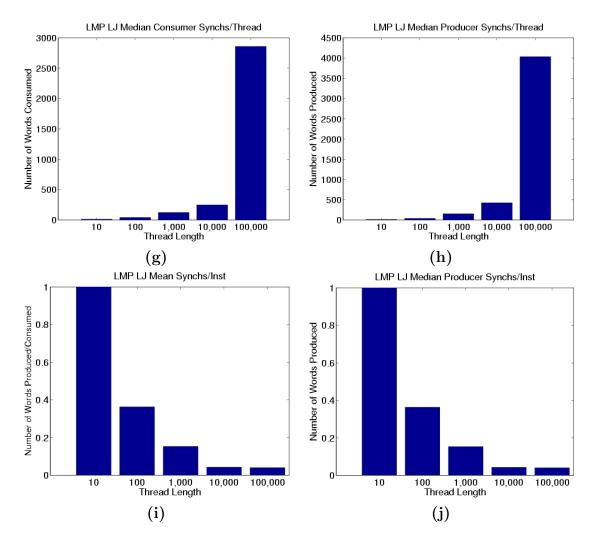

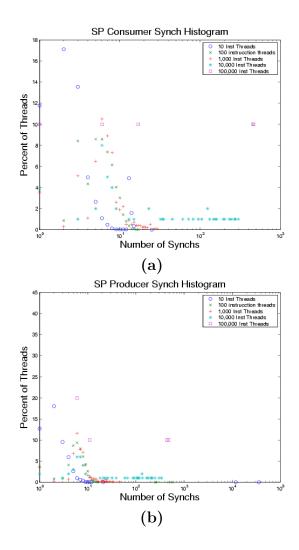

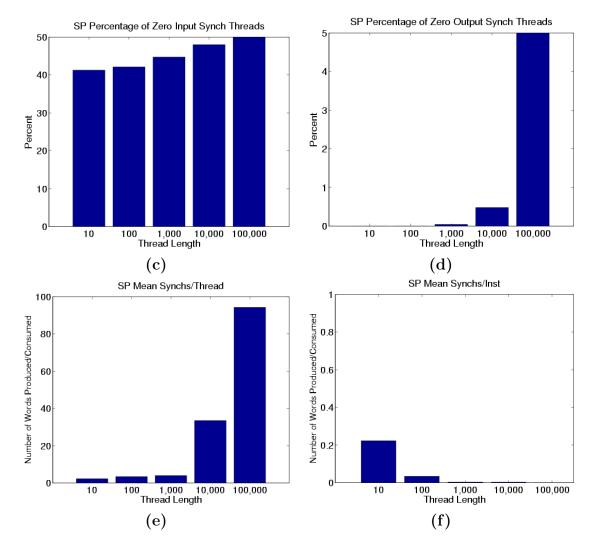

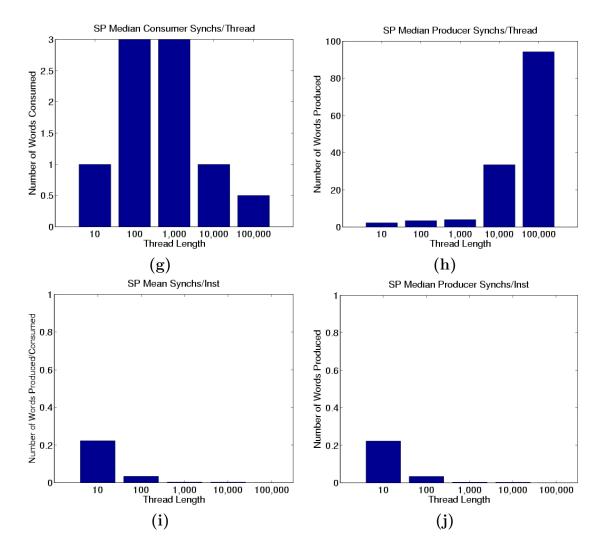

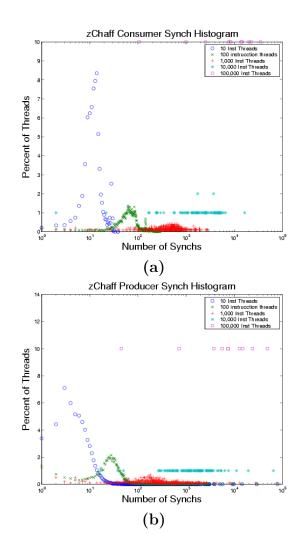

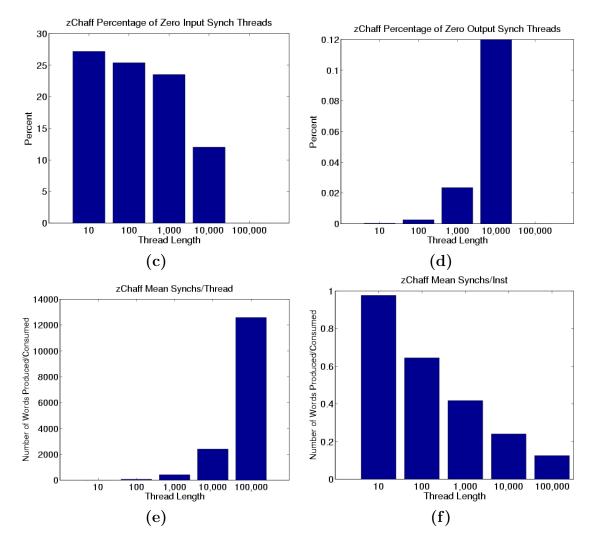

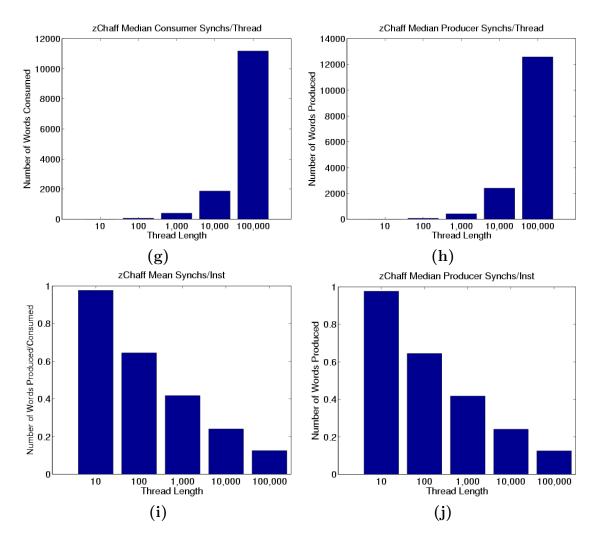

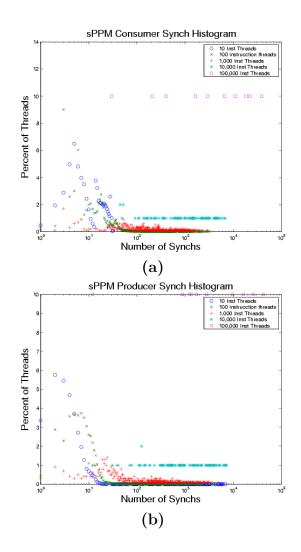

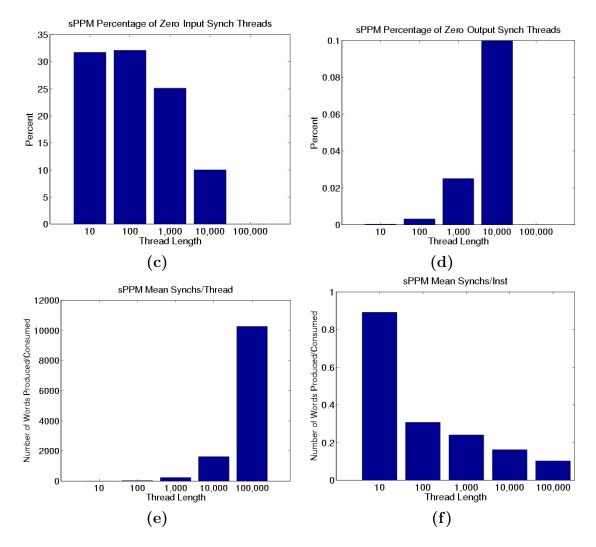

| 0.0   | 6.3.1 Mean Synchronization                                                                                                                                  |

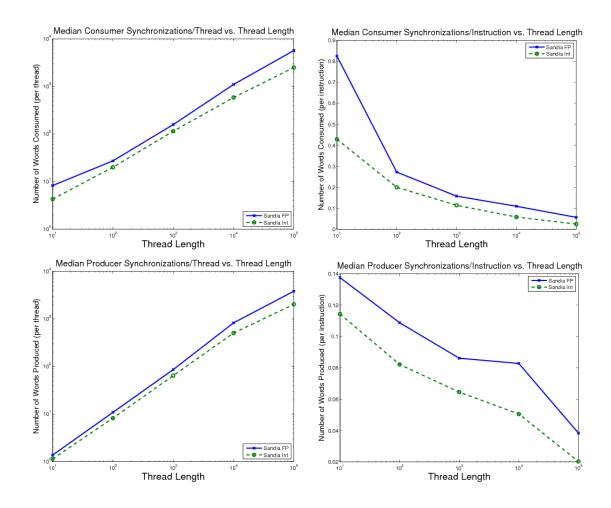

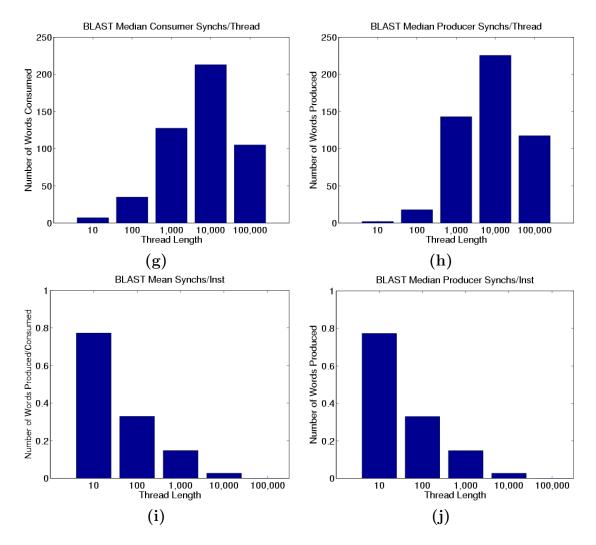

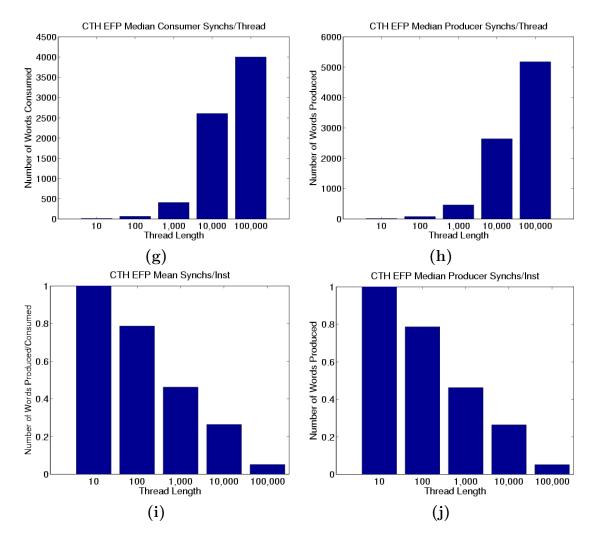

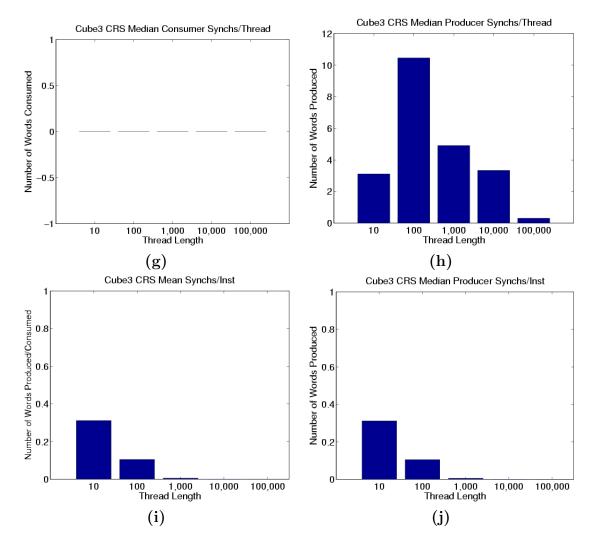

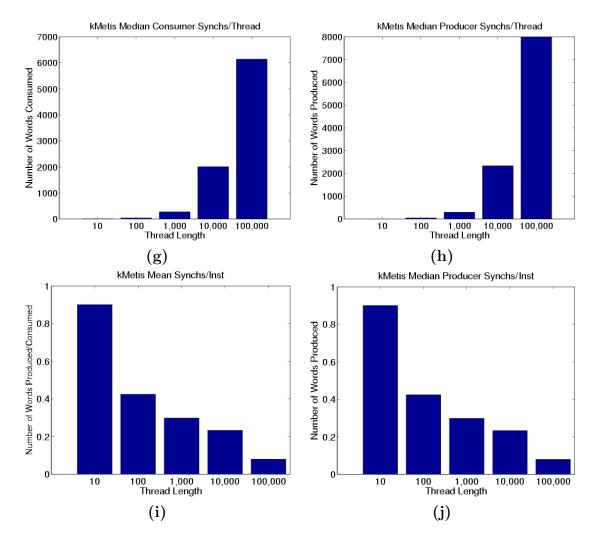

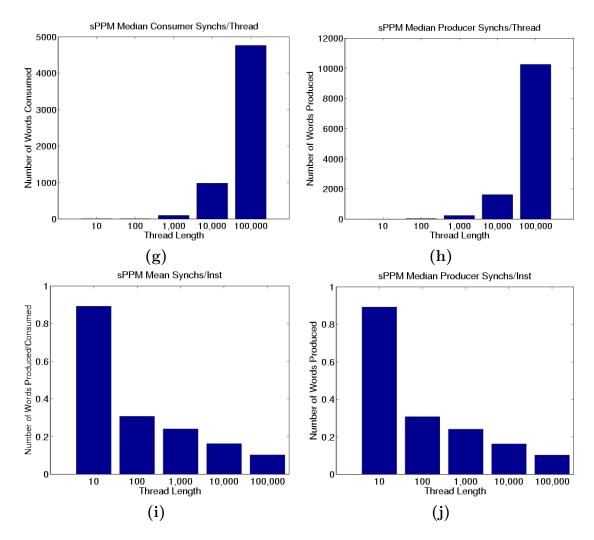

|       | 6.3.2 Median Synchronization Values                                                                                                                         |

|       | 6.3.3 Internal Computation                                                                                                                                  |

|       |                                                                                                                                                             |

| C 1   |                                                                                                                                                             |

| 6.4   | Conclusions                                                                                                                                                 |

|       |                                                                                                                                                             |

|       | $\mathbf{T} = \mathbf{T} \mathbf{T} \mathbf{T} \mathbf{T} \mathbf{T} \mathbf{T} \mathbf{T} \mathbf{T}$                                                      |

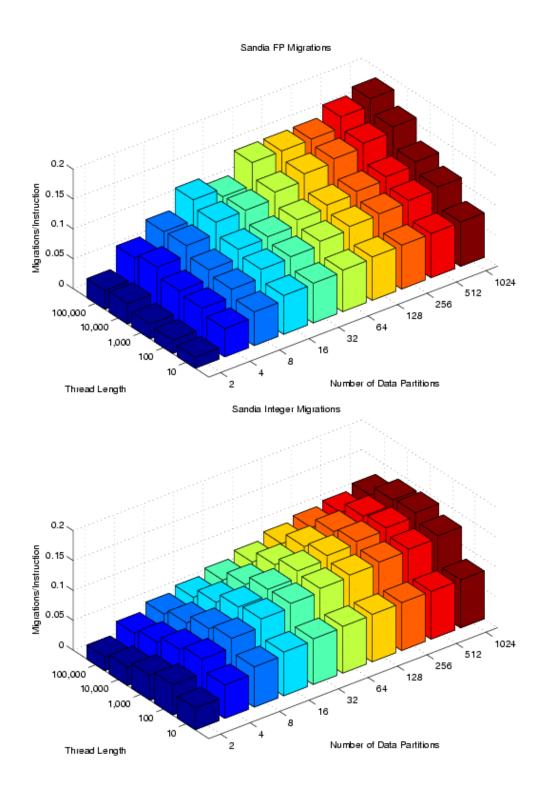

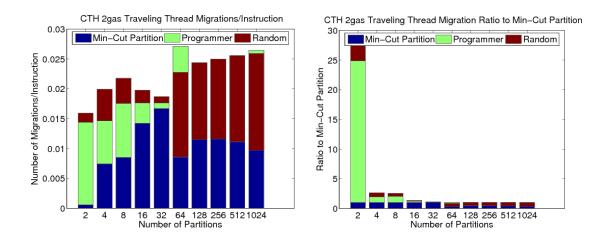

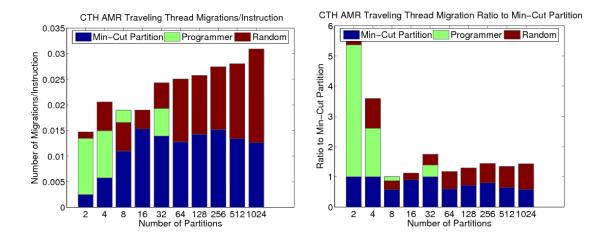

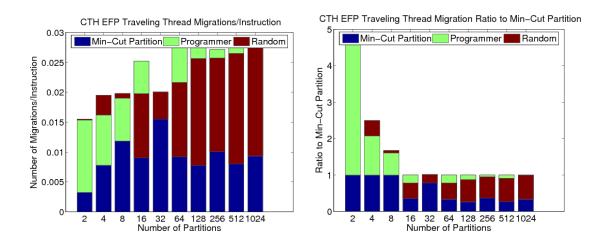

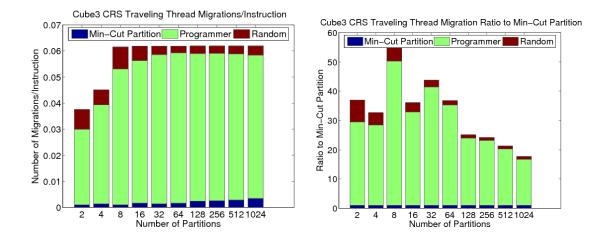

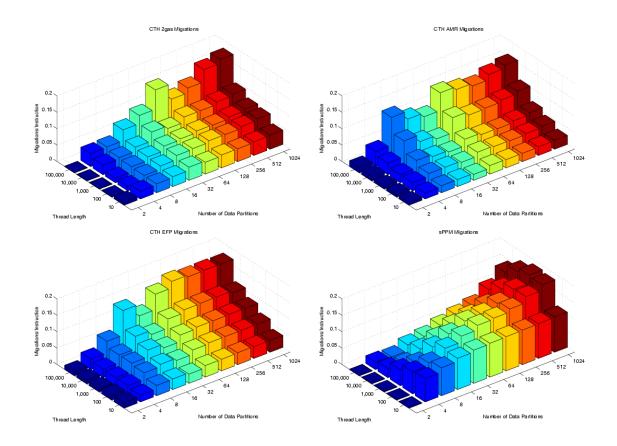

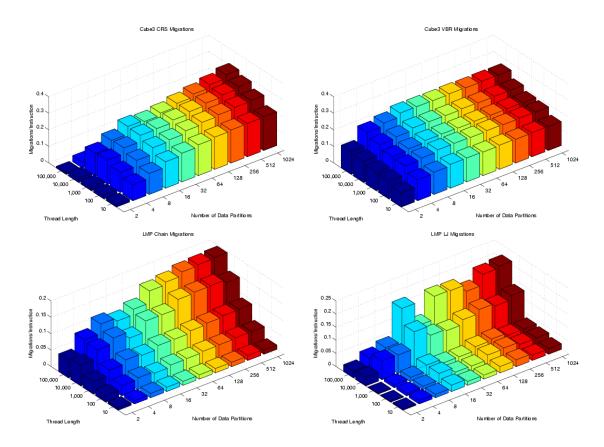

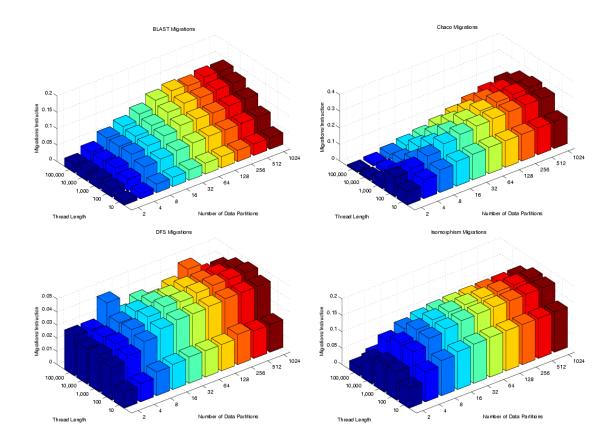

|       | TER 7: DATA PARTITIONING    124      124    125                                                                                                             |

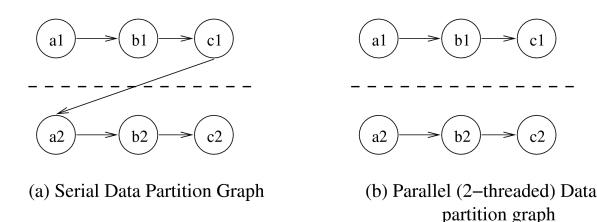

| 7.1   | Data Transition Graph                                                                                                                                       |

|       | 7.1.1 Serial Computation Graphs                                                                                                                             |

|       | 7.1.2 Parallel Computation Graphs                                                                                                                           |

| 7.2   | Data Transition Graph Partitioning                                                                                                                          |

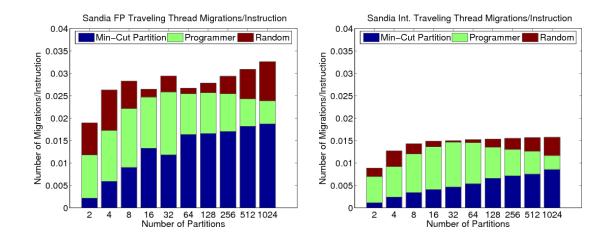

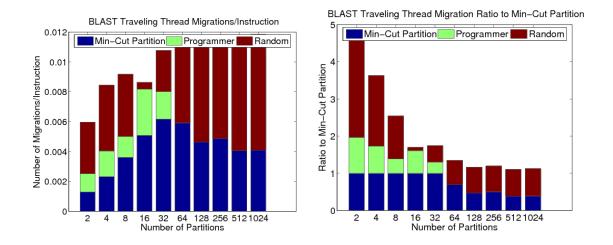

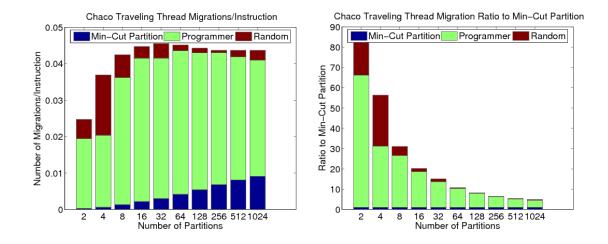

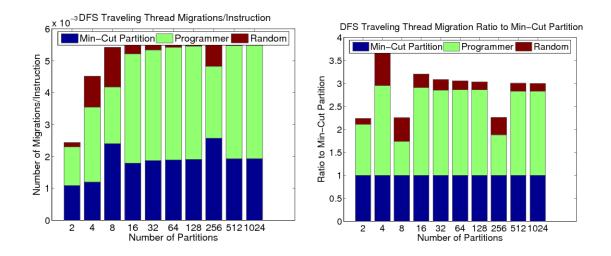

| 7.3   | Partitioning Results                                                                                                                                        |

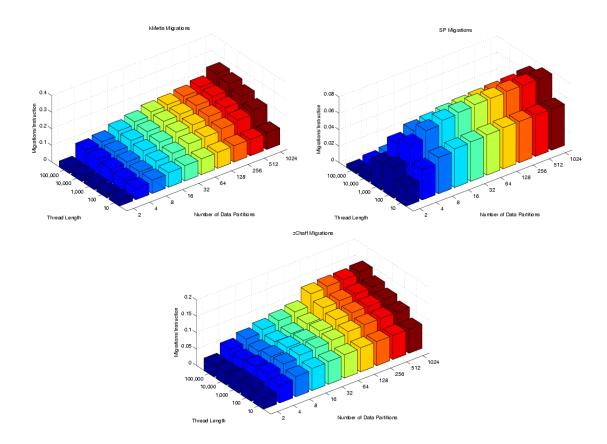

| 7.4   | Traveling Thread Results                                                                                                                                    |

| 7.5   | Comparison to a Conventional Processor                                                                                                                      |

| 7.6   | Conclusions                                                                                                                                                 |

|       |                                                                                                                                                             |

|       |                                                                                                                                                             |

| СНАРТ | YER 8: CONCLUSIONS    141                                                                                                                                   |

| 8.1   | The Traveling Thread Machine                                                                                                                                |

|       | 8.1.1 Thread Length                                                                                                                                         |

|       | 8.1.2 Thread Context Size                                                                                                                                   |

|       | 8.1.3 Synchronization                                                                                                                                       |

|       | 8.1.4 Migration                                                                                                                                             |

| 8.2   | Programming                                                                                                                                                 |

| 8.3   | Conclusions $\ldots \ldots \ldots$          |

| 8.4   | Future Work         152                                                                                                                                     |

| 0.4   |                                                                                                                                                             |

| APPENDIX A: FULL BENCHMARK CHARACTERISTIC DATA 156 |

|----------------------------------------------------|

| APPENDIX B: FULL DATAFLOW RESULTS                  |

| APPENDIX C: FULL THREADS RESULTS                   |

| APPENDIX D: FULL DATA PARTITIONING RESULTS         |

| BIBLIOGRAPHY                                       |

# FIGURES

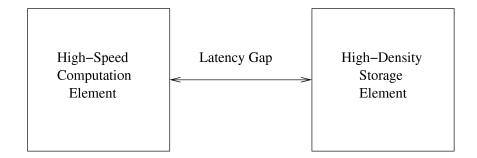

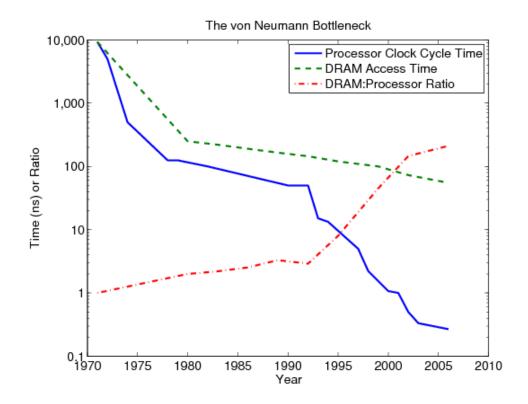

| 1.1  | The von Neumann Bottleneck                                                                    |

|------|-----------------------------------------------------------------------------------------------|

| 1.2  | The von Neumann Bottleneck                                                                    |

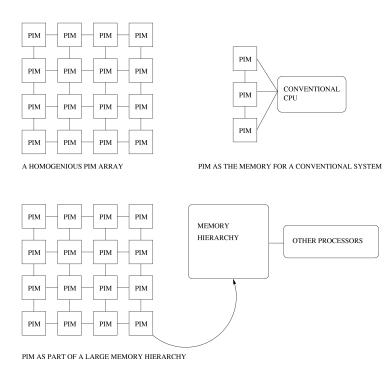

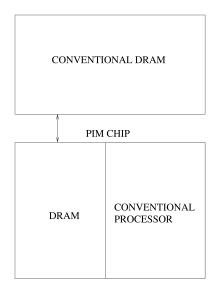

| 1.3  | PIM Configurations                                                                            |

| 1.4  | PIM Array Configurations                                                                      |

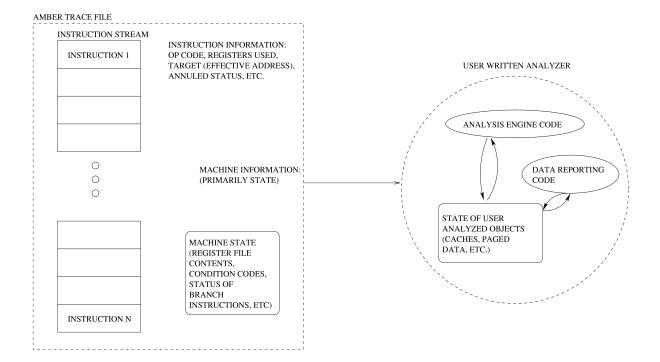

| 2.1  | Amber Simulations                                                                             |

| 2.2  | Conventional PIM Proposals                                                                    |

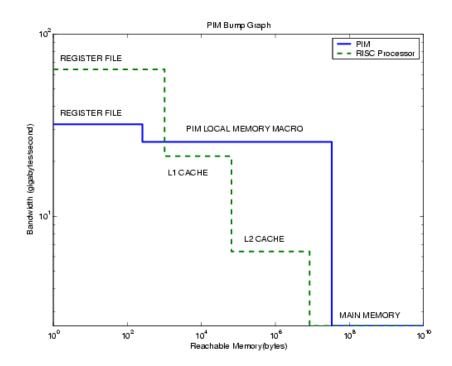

| 2.3  | PIM Memory Bandwidth                                                                          |

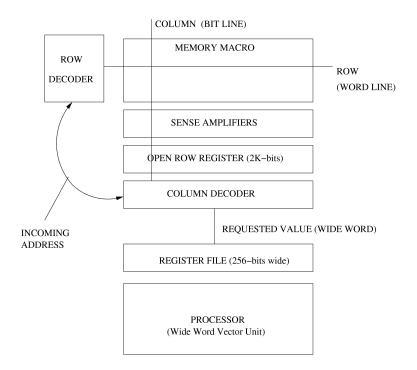

| 2.4  | Typical PIM Memory Layout                                                                     |

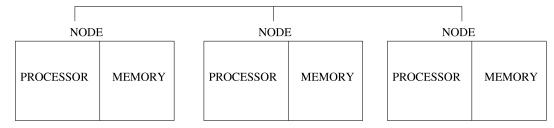

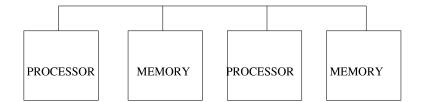

| 2.5  | DSM and SMP Systems                                                                           |

| 2.6  | A Typical CC-NUMA implementation                                                              |

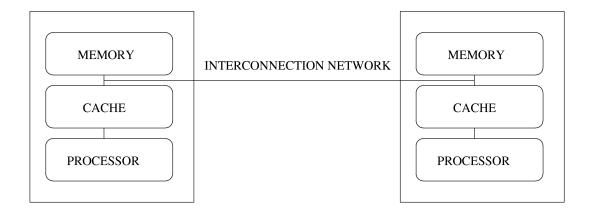

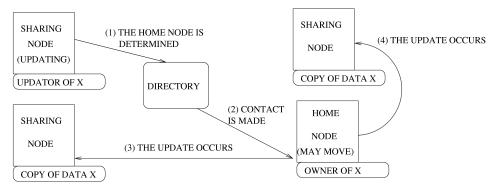

| 2.7  | A CC-NUMA machine during an update                                                            |

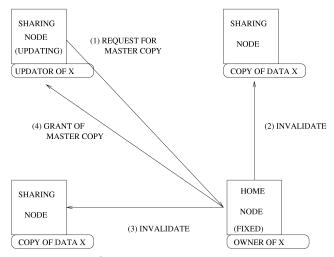

| 2.8  | A Typical COMA Machine                                                                        |

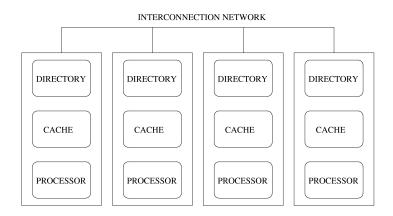

| 2.9  | A COMA machine during an update                                                               |

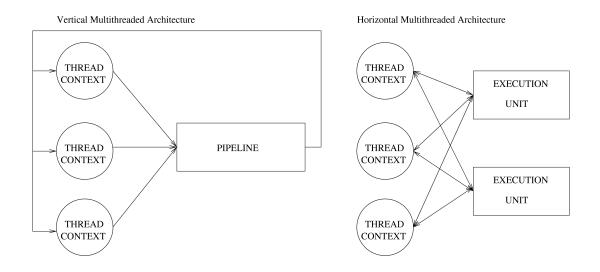

| 2.10 | Vertical and Horizontal Multithreaded Systems                                                 |

| 2.11 | Types of Processor and Memory Distributions                                                   |

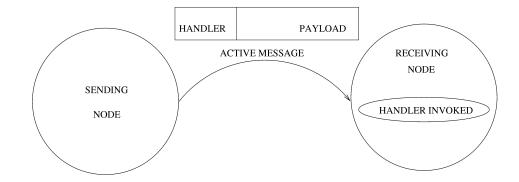

| 2.12 | Active Messages                                                                               |

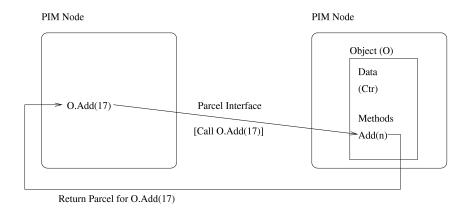

| 2.13 | Actor Based Language Message Passing                                                          |

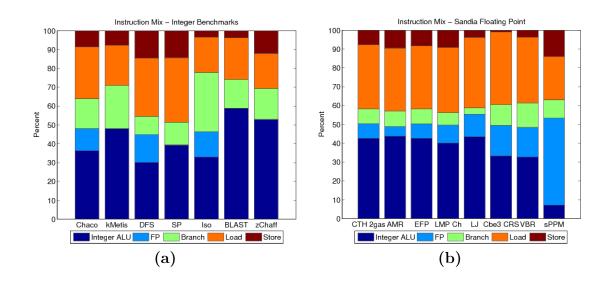

| 3.1  | Benchmark Suite Mean Instruction Mix                                                          |

| 3.2  | Integer Instruction to Floating Point Instruction Ratios for the Sandia<br>and SPEC FP Suites |

| 3.3  | Working Set Miss Rate Interpretation                                                          |

| 3.4  | Mean Working Set Miss Rates                                                                   |

| 3.5  | Mean Working Set Memory Bytes Consumed per Flop Executed                                                                                                                                                                        | 69  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.6  | Mean Benchmark Spatial Locality Results                                                                                                                                                                                         | 71  |

| 3.7  | Mean Benchmark Spatial Locality Overhead Results                                                                                                                                                                                | 72  |

| 4.1  | Carpetbag Cache Example                                                                                                                                                                                                         | 79  |

| 4.2  | This example traverses a linked list. The pseudo-code is given on<br>the left, with pseudo-assembly on the right. The assembly assumes<br>MIPS-like instructions, with registers given names (prefaced with \$)<br>for clarity. | 81  |

| 4.3  | Explicit Thread Migration                                                                                                                                                                                                       | 85  |

| 4.4  | Migration via an exception                                                                                                                                                                                                      |     |

| 4.5  | A writer incrementing the data value of a node in the linked list                                                                                                                                                               | 89  |

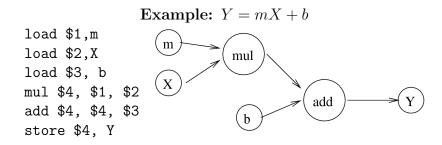

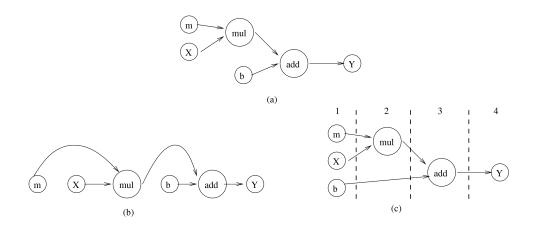

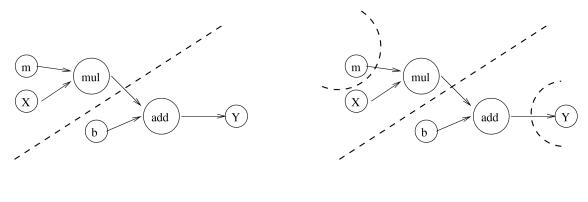

| 5.1  | The dataflow graph and pseudo-assembly language implementing the computation of $Y = mx + b$                                                                                                                                    | 92  |

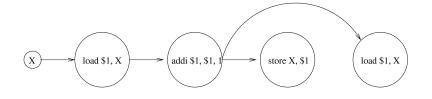

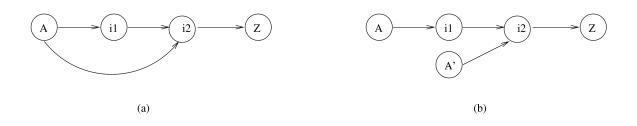

| 5.2  | Dataflow Dependencies Passing Through Memory                                                                                                                                                                                    | 94  |

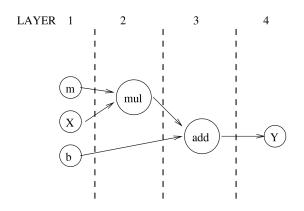

| 5.3  | The dataflow graph from Figure 5.1 assigned a schedule that allows instructions to execute only after each of their data dependencies are satisfied.                                                                            | 96  |